"미리넷 MVL100D4-LR VDSL"의 두 판 사이의 차이

잔글 |

잔글 |

||

| 107번째 줄: | 107번째 줄: | ||

image:vdsl01_014.jpg | Broadcom AC201A1KML Ethernet Chip | image:vdsl01_014.jpg | Broadcom AC201A1KML Ethernet Chip | ||

</gallery> | </gallery> | ||

| − | <li> [[수정 발진기]] 5x7mm, 35.3280MHz DSL용, UART에서는 baud속도의 정수비(64×552000 baud, 256×138000 baud, 460×38400 baud or 460×32×1,200 baud), VDSL에서는 2x17.664MHz, ADSL에서는 16x2.208MHz(ADC sampling rate) | + | <li> [[세라믹 패키지 수정 발진기]] |

| + | <ol> | ||

| + | <li>5x7mm, 35.3280MHz DSL용, UART에서는 baud속도의 정수비(64×552000 baud, 256×138000 baud, 460×38400 baud or 460×32×1,200 baud), VDSL에서는 2x17.664MHz, ADSL에서는 16x2.208MHz(ADC sampling rate) | ||

<gallery> | <gallery> | ||

image:vdsl01_021.jpg | CPE20FDDM 35.328 SUNNY | image:vdsl01_021.jpg | CPE20FDDM 35.328 SUNNY | ||

image:vdsl01_022.jpg | image:vdsl01_022.jpg | ||

| − | image:vdsl01_023.jpg | | + | image:vdsl01_023.jpg | [[심 용접]] 때 리드가 많이 틀어져 있다. |

| − | image:vdsl01_024.jpg | | + | image:vdsl01_024.jpg | 단단하게 경화되는 실버 에폭시 [[도전성 접착제]]를 사용했다. |

</gallery> | </gallery> | ||

| + | </ol> | ||

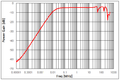

<li>LINE 포트와 TEL 포트간 경로 주파수 특성, | <li>LINE 포트와 TEL 포트간 경로 주파수 특성, | ||

<gallery> | <gallery> | ||

2025년 2월 19일 (수) 23:10 기준 최신판

미리넷 MVL100D4-LR VDSL

- 전자부품

- 전화기

- VDSL 디지탈가입자회선

- 미리넷 MVL100D4-LR VDSL - 이 페이지

- VDSL 디지탈가입자회선

- 전화기

- 미리넷 MVL100D4-LR DSL

- 사용자 설명서 - 17p

- DMT(Discrete Multi-tone) 전송방식으로 3km까지 하향 최대 100Mbps, 상향 50Mbps

- 외관

- 보드 앞면 및 뒷면

- 아날로그 파트

- 전체

- 과전류차단하는 래디얼 리드 P-PTC

- Fuzetec회사 FRX75

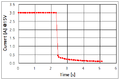

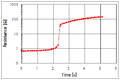

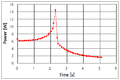

- 66311B 파워서플라이로 @15V T-I 그래프

- Fuzetec회사 FRX75

- CMF, TE Connectivity, COEV magnetics brand, C9606S

- 사진

- 측정

- Advantest R3753BH 네트워크분석기로 측정 데이터

- 사진

- 전화기 포트와 연결되는 1:1 트랜스포머 측정

- 사진

- Advantest R3753BH 네트워크분석기로 측정 데이터

- 사진

- Pulse BX4141W, RF 트랜스포머 측정

- 사진

- Advantest R3753BH 네트워크분석기로 측정 데이터,

- 사진

- VLR-CPE4-KT NT-T- 하이브리드IC

- 전체

- 디지털 파트

- 세라믹 패키지 수정 발진기

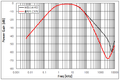

- LINE 포트와 TEL 포트간 경로 주파수 특성,

- LINE 포트와 DSL용 IC간 경로 주파수 특성

- 전화선 커넥터 추가 및 전화선 추가 길이에 따라

- 사용자 설명서 - 17p